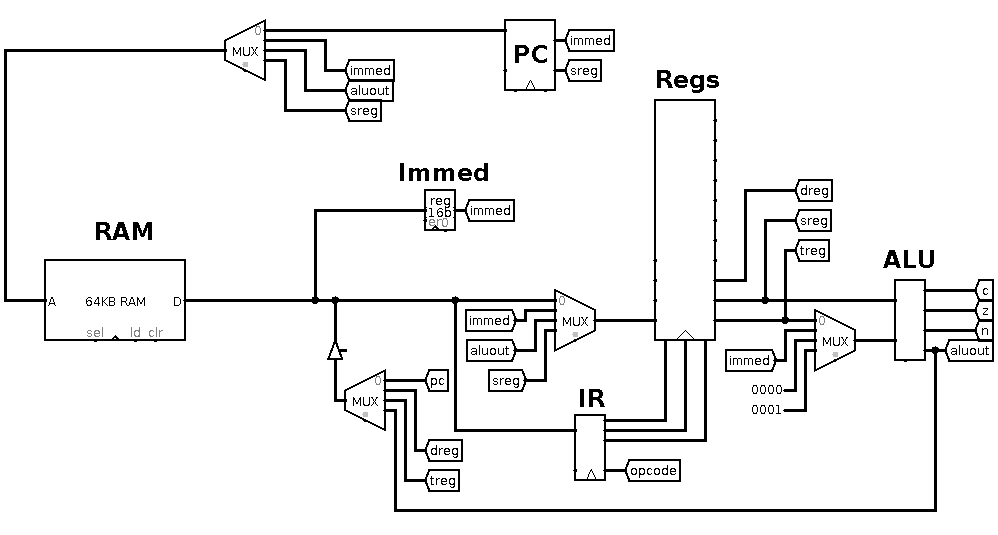

GitHub - tffdev/TSYS: 🍵🖥 A simple 12 bit Logisim RISC CPU architecture + a low-level programming language + an assembler

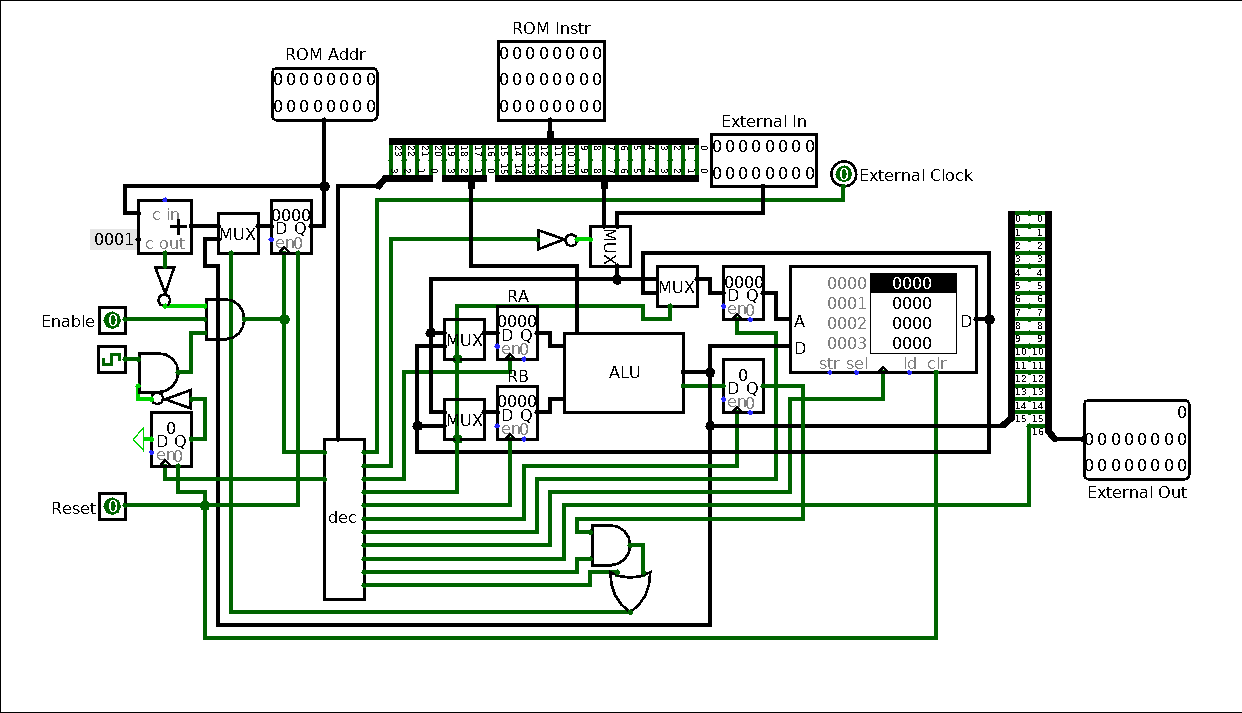

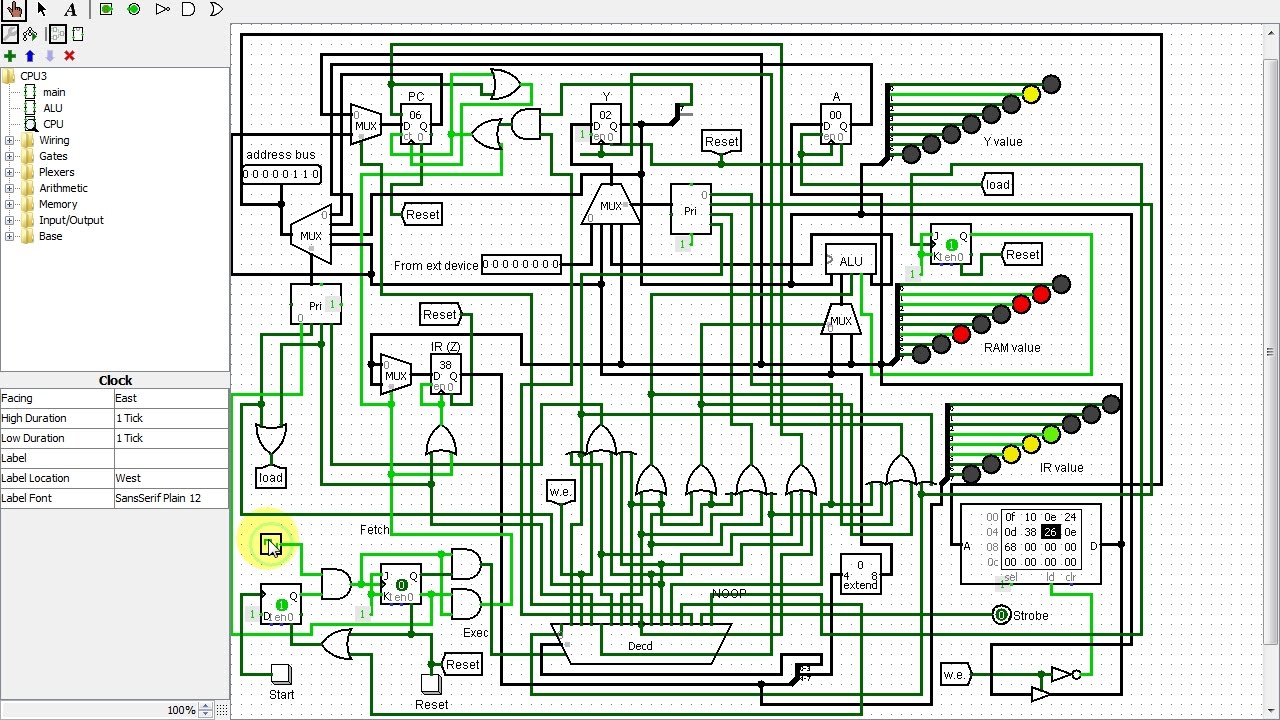

Design and implementation 8 bit CPU architecture on Logisim for undergraduate learning support | Semantic Scholar

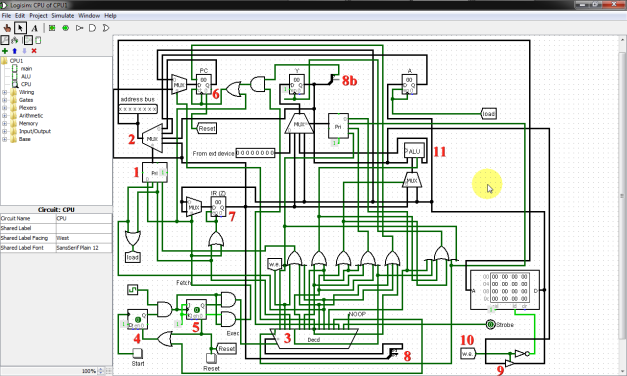

cpu - Logisim: Implementing a control unit for "Addition", "Logic bitwise AND" and "right logic shift" in ALU - Electrical Engineering Stack Exchange

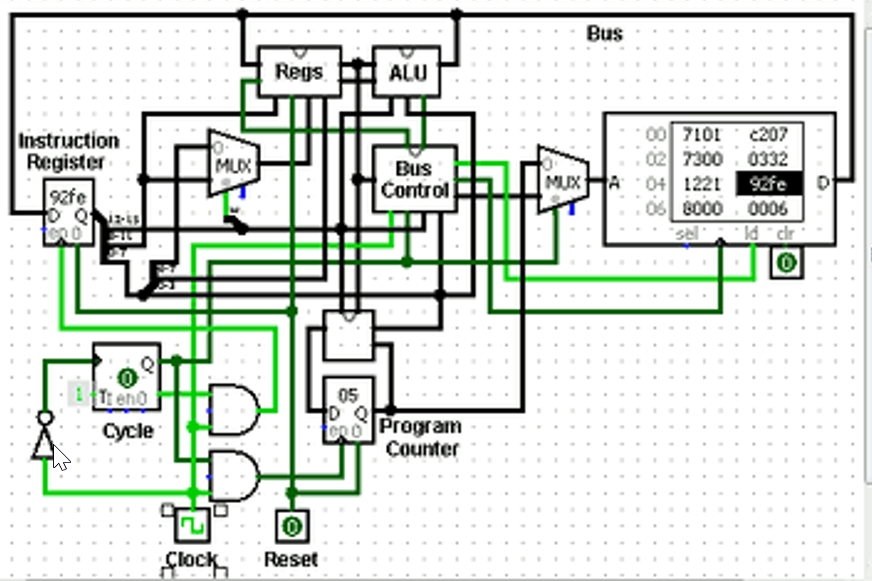

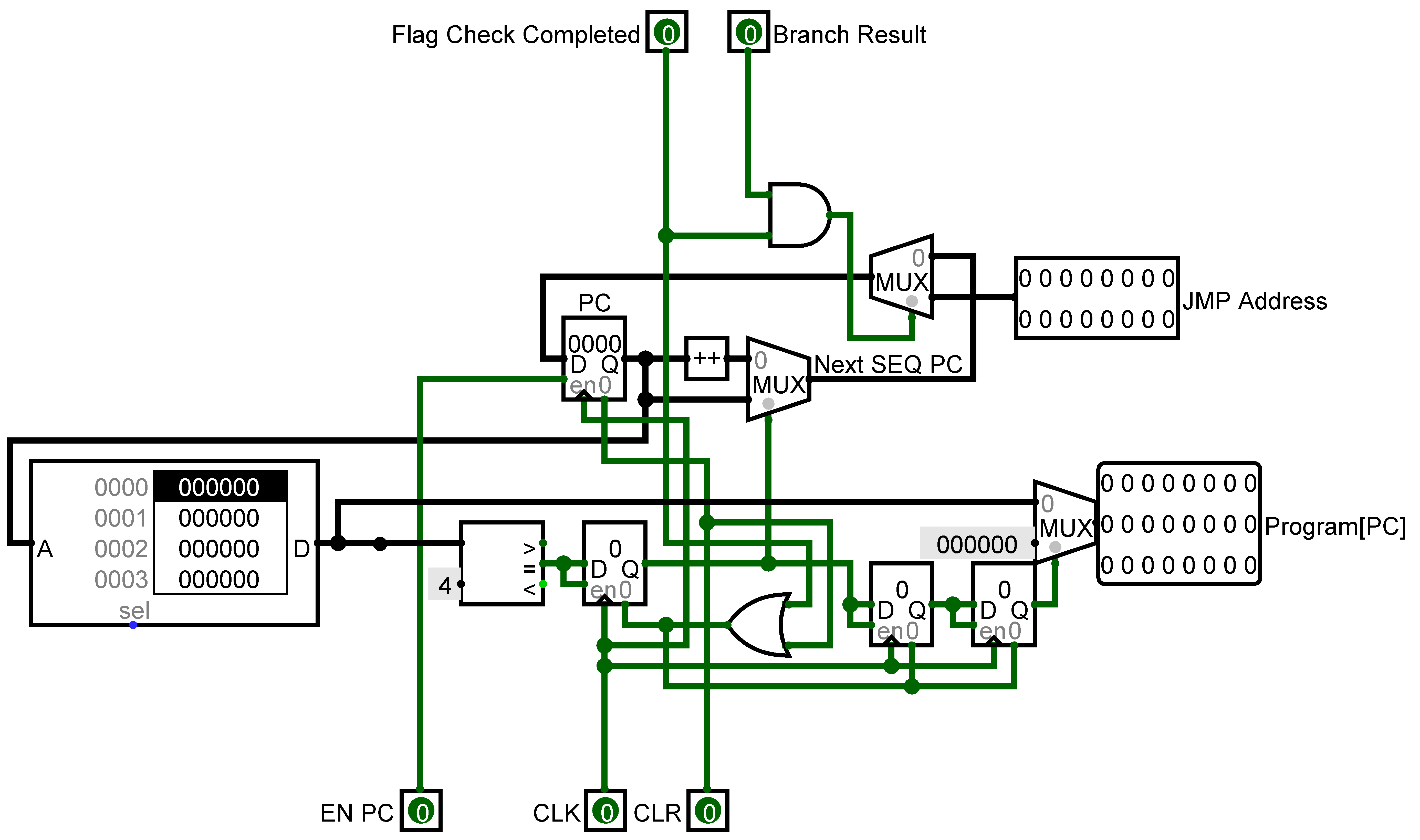

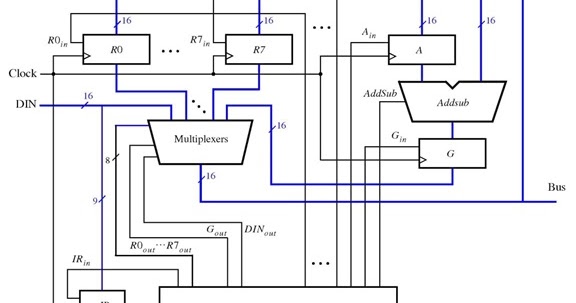

![JFS] Custom 16-bit CPU : r/logisim JFS] Custom 16-bit CPU : r/logisim](https://external-preview.redd.it/R8sLHGlI0NNArWi_vRcOb9z273z7acjE-npwMdxXOiA.png?auto=webp&s=3519e69c64830d4f4855fbbf4f158cb7dcd84e3b)